# ALTERNATIVE LITHOGRAPHY STRATEGIES for FLEXIBLE ELECTRONICS

#### Thesis committee members:

Prof. dr. G. van der Steenhoven University of Twente (chairman)

Prof. dr. ir. J. Huskens University of Twente (supervisor)

Prof. dr. G. H. Celinek University of Twente (supervisor)

Dr. ir. G. H. Gelinck Holst Centre / TNO Mag. dr. B. Stadlober Joanneum Research

Prof. dr. D. J. Broer Technical University of Eindhoven

Prof. dr. ir. W. G. van der Wiel

Prof. dr. J. G. E. Gardeniers

University of Twente

University of Twente

University of Twente

The research described in this Ph.D. thesis was financed by the program "Patterning for Flexible Systems" of the Holst Centre / TNO in Eindhoven.

Publisher: Wöhrmann Print Service, Zutphen, The Netherlands.

ISBN 978-90-365-3371-3

doi: 10.3990/1.9789036533713

Copyright © Pieter Frederik Moonen, Enschede, 2012.

All rights reserved. No part of this work may be reproduced by print, photocopy or any other means without prior permission in writing from the author.

## ALTERNATIVE LITHOGRAPHY STRATEGIES FOR FLEXIBLE ELECTRONICS

#### **PROEFSCHRIFT**

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof. dr. H. Brinksma,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op woensdag 4 juli 2012 om 14.45 uur

door

Pieter Frederik Moonen

geboren op 29 februari 1984 te Leiden Dit proefschrift is goedgekeurd door:

Promotor: Prof. dr. ir. J. Huskens

#### **Table of Contents**

| Chapter 1: General Introduction Stratagies for E                      |               |

|-----------------------------------------------------------------------|---------------|

| Chapter 2: High-Resolution Patterning Strategies for F<br>Electronics |               |

| 2.1 Introduction                                                      | 6             |

| 2.2 Conventional Mass-Printing Techniques                             |               |

| 2.2.1 Flexographic Printing                                           | 10            |

| 2.2.2 Gravure Printing                                                | 13            |

| 2.2.3 Offset Printing                                                 | 15            |

| 2.2.4 Screen Printing                                                 | 16            |

| 2.2.5 Inkjet Printing                                                 | 18            |

| 2.3 High-Resolution Patterning                                        | 20            |

| 2.3.1 Photolithography                                                | 21            |

| 2.3.2 Towards Alternative Methods for Hig                             | h-Resolution  |

| Patterning                                                            | 23            |

| 2.4 Soft Lithography                                                  | 25            |

| 2.4.1 Microcontact Printing (μCP)                                     | 26            |

| 2.4.2 Micromolding in Capillaries (MIMIC).                            | 28            |

| 2.4.3 Micro and Nanotransfer Printing (μΤΙ                            | ond nTP)30    |

| 2.5 Nanoimprint Lithography                                           | 33            |

| 2.6 Concluding Remarks                                                | 38            |

| 2.7 References                                                        | 43            |

| Chapter 3: Double-Layer Imprint Lithography on Wafe                   | ers and Foils |

| from the Submicrometer to the Millimeter Scale                        | 55            |

| 3.1 Introduction                                                      | 56            |

| 3.2 Results and Discussion                                            |               |

| 3.2.1 Design and Process Scheme                                       | 58            |

| 3.2.2 Regular NIL                                                     | 59            |

|              | 3.2.3 Reverse NIL                                | 61  |

|--------------|--------------------------------------------------|-----|

|              | 3.2.4 Double-Layer NIL                           | 63  |

| 3.3 C        | onclusions                                       | 69  |

| 3.4 E        | xperimental Section                              |     |

|              | 3.4.1 Materials and Methods                      | 70  |

|              | 3.4.2 Preparation of Fluorinated Molds           | 70  |

|              | 3.4.3 Resist Deposition                          | 70  |

|              | 3.4.4 Thermal Imprinting                         | 71  |

|              | 3.4.5 Residual Layer Removal                     | 71  |

|              | 3.4.6 Direct Etching                             | 71  |

|              | 3.4.7 Lift-Off                                   | 71  |

| 3.5 R        | eferences                                        | 72  |

| Chapter 4: A | Common-Gate Thin-Film Transistor on Poly(ethyl   | ene |

| naphthalate  | e) Foil using Step-and-Flash Imprint Lithography | 75  |

| 4.1 Ir       | ntroduction                                      | 76  |

| 4.2 R        | esults and Discussion                            |     |

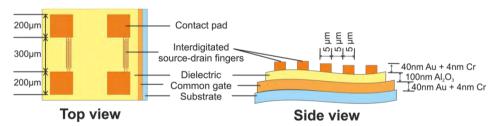

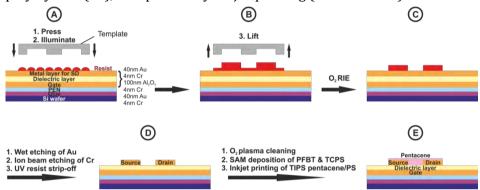

|              | 4.2.1 Design and Process Scheme                  | 78  |

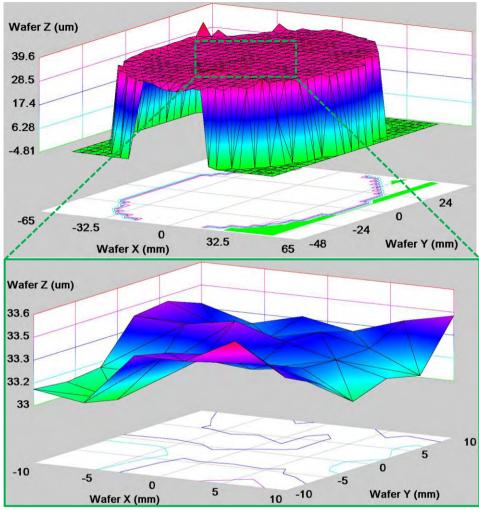

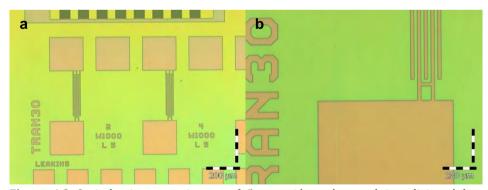

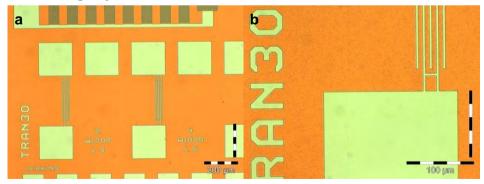

|              | 4.2.2 Fabrication                                | 80  |

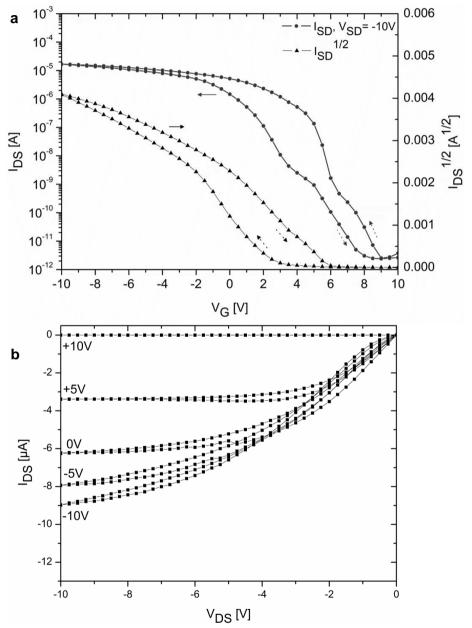

|              | 4.2.3 Electrical Characterization                | 86  |

| 4.3 C        | onclusions                                       | 89  |

| 4.4 E        | xperimental Section                              |     |

|              | 4.4.1 Materials and Methods                      | 90  |

|              | 4.4.2 Foil-on-Carrier (FOC)                      | 90  |

|              | 4.4.3 Step-and-Flash Imprint Lithography (SFIL)  | 91  |

|              | 4.4.4 Residual Layer Removal                     | 91  |

|              | 4.4.5 Direct Etching                             | 92  |

|              | 4.4.6 Resist Strip-Off                           | 92  |

|              | 4.4.7 Self-Assembled Monolayers                  | 92  |

|              | 4.4.8 Semiconductor Deposition                   | 92  |

| 4.5 R        | eferences                                        | 93  |

| on Si and Poly(ethylene naphthalate) Foil Exclusively Patterne | Ŭ     |

|----------------------------------------------------------------|-------|

| Nanoimprint Lithography                                        | •     |

|                                                                |       |

| 5.1 Introduction                                               | 98    |

| 5.2 Results and Discussion                                     |       |

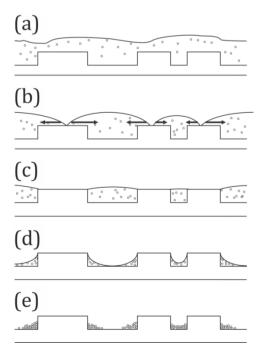

| 5.2.1 Design and Process Scheme                                | 100   |

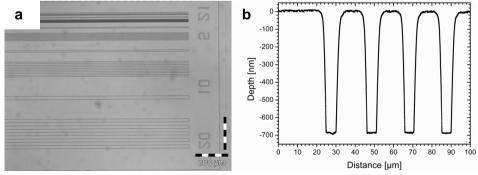

| 5.2.2 Fabrication                                              | 102   |

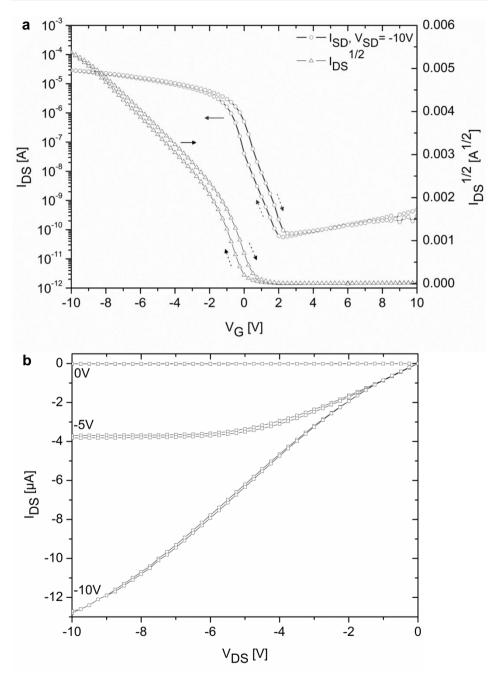

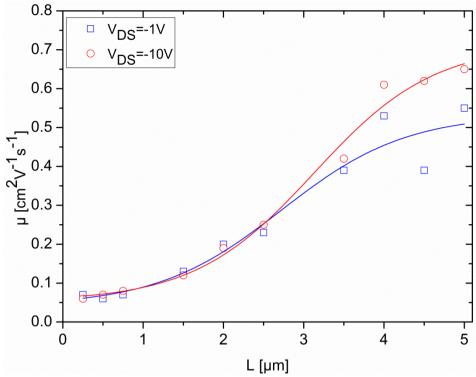

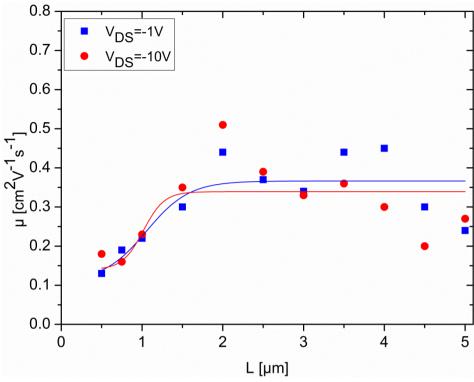

| 5.2.3 Electrical Characterization                              | 109   |

| 5.3 Conclusions                                                | 116   |

| 5.4 Experimental Section                                       |       |

| 5.4.1 Materials and Methods                                    | 116   |

| 5.4.2 Foil-on-Carrier (FOC)                                    | 117   |

| 5.4.3 Step-and-Flash Imprint Lithography (SFIL)                | 117   |

| 5.4.4 Dry Etching                                              | 117   |

| 5.4.5 Dielectric Deposition                                    | 118   |

| 5.4.6 Self-Assembled Monolayers                                | 118   |

| 5.4.7 Semiconductor Deposition                                 | 118   |

| 5.5 References                                                 | 119   |

| Chapter 6: Selective Material Deposition in Open Microchanne   | ls123 |

| 6.1 Introduction                                               | 124   |

| 6.2 Results and Discussion                                     |       |

| 6.2.1 Process Scheme                                           | 127   |

| 6.2.2 Filling Mechanism in Open Microchannels                  | 130   |

| 6.2.3 Metal Wires by Functional Solute Deposition              | 132   |

| 6.3 Conclusions                                                | 133   |

| 6.4 Experimental Section                                       |       |

| 6.4.1 Materials                                                | 134   |

| 6.4.2 Template Manufacturing                                   | 134   |

| 6.4.3 Thermal Imprint Lithography                              | 134   |

| 6.4.4 Material Deposition                                      | 135   |

| 6.5 References                                                 | 135   |

| Chapter 7: Soft-Lithographic Patterning of Room Temperatur |         |

|------------------------------------------------------------|---------|

| Sintering Ag Nanoparticles on Foil                         | 137     |

| 7.1 Introduction                                           | 138     |

| 7.2 Results and Discussion                                 | 140     |

| 7.2.1 Ag Wires on PET by MIMIC                             | 142     |

| 7.2.2 Embedded Ag Wires on PET Foil                        | 147     |

| 7.2.3 Sol-Gel Printed Ag Dots on an Elastomeric Sur        | face150 |

| 7.3 Conclusions                                            | 153     |

| 7.4 Experimental Section                                   |         |

| 7.4.1 Ag NP Synthesis                                      | 154     |

| 7.4.2 Ag NP Sintering                                      | 155     |

| 7.4.3 Preparation of PDMS Molds                            | 155     |

| 7.4.4 Preparation of SU8 Trenches on PET                   | 155     |

| 7.4.5 Hydrogel Stamps                                      | 156     |

| 7.5 References                                             | 157     |

| Summary and Outlook                                        | 159     |

| Samenvatting en vooruitzicht                               | 165     |

| Acknowledgements                                           | 171     |

| Curriculum Vitae                                           | 175     |

#### Chapter 1

#### **General Introduction**

Flexible electronics is an area of research and development that foresees the fabrication of faster, lighter, thinner, bendable and cheaper devices manufactured on low-cost polymeric foils. Classical and new patterning strategies for high-throughput, large-volume roll-to-roll (or reel-to-reel) manufacturing lines, which are known from newspaper printers, are being developed to further reduce manufacturing costs. Examples of inventions and products soon to hit the market are flexible organic light-emitting diode- (OLED-)based displays,<sup>[1-3]</sup> radio-frequency identification (RFID) tags,<sup>[4, 5]</sup> and organic solar cells (OSCs).<sup>[6-8]</sup>

Renowned patterning techniques face new challenges when patterning high-resolution flexible electronics, not necessarily originating from the small dimensions of the device, but from deformations and the dimensional instability of the polymeric foils. Reversibly gluing of the foil onto a carrier (foil-on-carrier; FOC) improves the mechanical and in-plane stability during processing. As a low-cost patterning technique with routine nanometer patterning capabilities, nanoimprint lithography (NIL) has been identified as one of the ten next-generation lithography techniques to manufacture high-density integrated circuits and optics. The capability of NIL to pattern complex electronic devices on flexible substrates is studied in this thesis (Chapters 3-5). Flexible thin-film transistor demonstrators are patterned on poly(ethylene naphthalate) (PEN) foil by UV NIL, and their electrical performance is determined.

A restriction to the patterning process and materials introduced by the cheap polymeric foils, is the limitation of the temperature window to around 150°C.<sup>[9]</sup> The low glass transition temperature of the polymeric foils

(e.g. ~70-85°C for PET<sup>[10]</sup>) requires alternative deposition techniques and newly engineered materials. Especially high-*k* dielectrics and highly conductive, metallic structures need to be deposited and patterned on polymeric foils. The sintering behavior and resulting conductivity of metallic precursor inks are often studied for inkjet-printed features. Alternative lithographic processes to fabricate metallic, conductive structures from metallic precursor materials are presented in Chapters 6 and 7, which simultaneously allow the directed deposition of materials in channels without alignment. Currently, the reported top-down methods aim to make self-aligned TFTs by smartly masking the different layers of the electronic device.<sup>[11-14]</sup> The processes studied here can be a first step towards a solution-based, self-aligned TFT.

The historical development of the first mass-printing strategies to highresolution, alternative patterning techniques is reviewed in Chapter 2. Its main focus is on large-area patterning of flexible electronics. Patterning techniques are compared, and their individual benefits and limitations discussed. The three most promising soft lithographic techniques in largearea printing, and the family of NIL, are described from the viewpoint of flexible electronics.

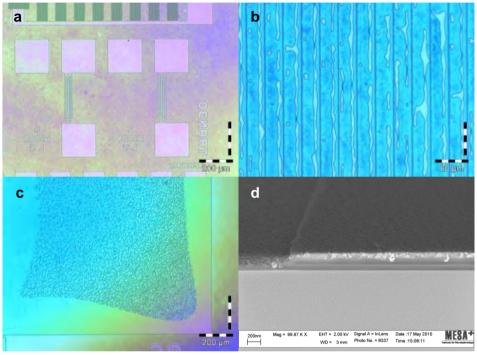

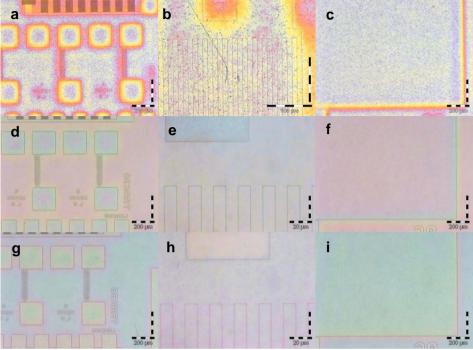

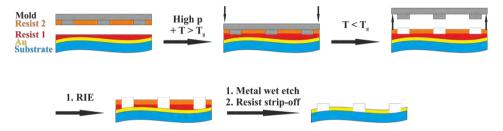

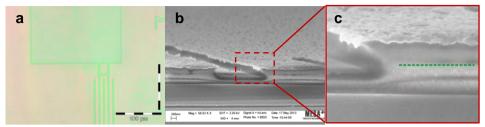

A novel thermal imprint process on Si and foil is presented in Chapter 3, capable of imprinting structures simultaneously from the submicron to the millimeter scale. With the new thermal imprint process, many resist combinations can be employed for tailored nanofabrication. In the example given, two resists with different etch resistivities are combined, allowing the complete removal of an inhomogeneous residual layer on foil.

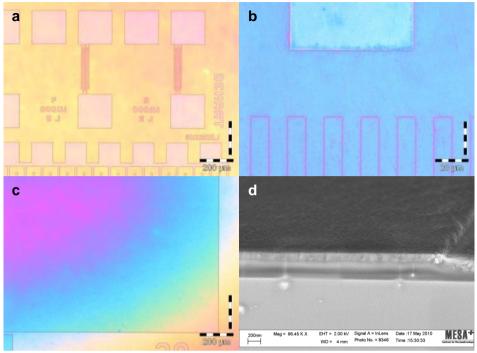

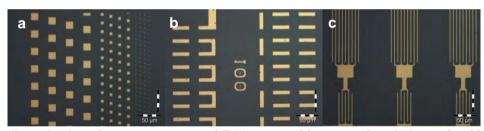

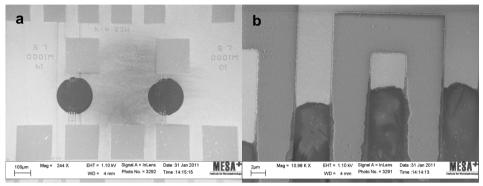

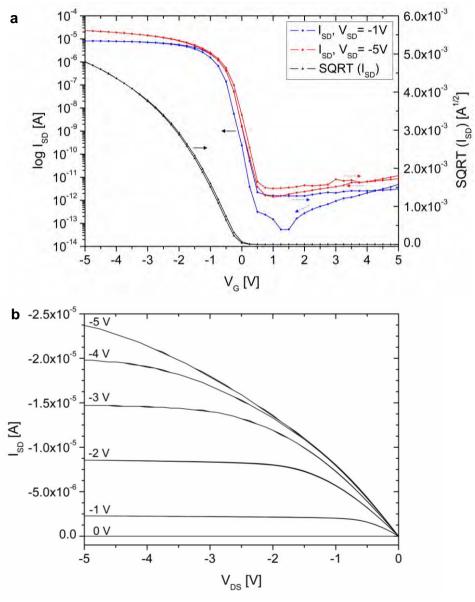

In Chapter 4, the source-drain layer of a flexible TFT demonstrator is patterned by UV NIL. A thin and relatively homogeneous residual layer thickness is obtained with a newly developed FOC system, obtained by hot embossing. The electrical performance is compared to state-of-the-art photolithographically fabricated flexible TFTs.

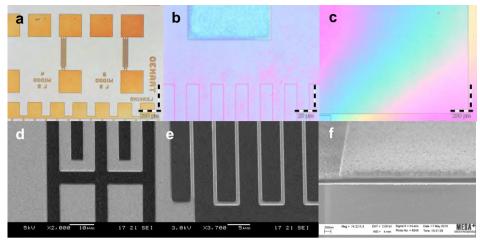

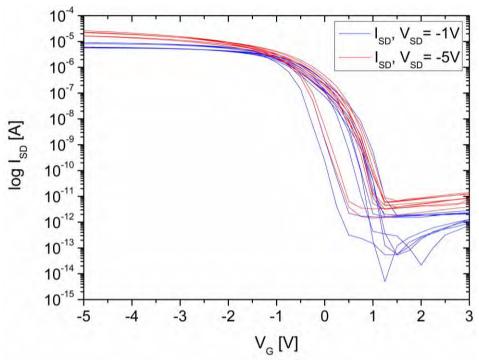

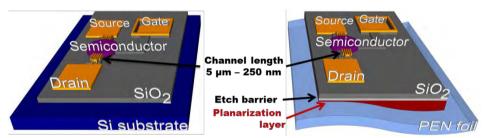

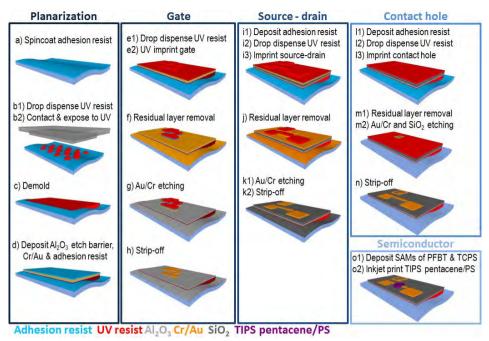

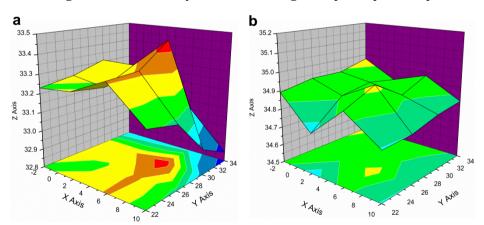

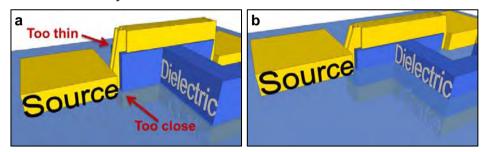

All three layers of a flexible TFT demonstrator, presented in Chapter 5, are patterned with UV NIL in a multistep imprinting process. The waviness of the FOC is further reduced by introduction of a novel, step-and-flash imprinted planarization layer. The residual layer thickness and distribution is thereby reduced. Flexible TFTs with channel lengths from 5  $\mu$ m down to 250 nm are presented and their electrical performance is discussed.

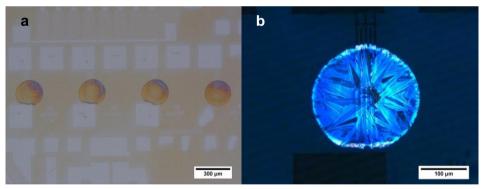

The filling mechanism of solutes in open microchannels formed by embossing of an epoxy resist on PET foil is studied in Chapter 6. The channel width-dependent filling and drying behavior is visualized by adding a fluorescent dye as the solute. Selective deposition of metallic precursor materials in the open microchannels is used to grow copper microwires from solution.

The soft lithographic patterning behavior of room temperature-sintering poly(acrylic acid)-capped silver nanoparticle dispersions is studied in Chapter 7. Silver wires are patterned on PET foil by micromolding in capillaries (MIMIC), and embedded silver wires are fabricated by selective filling of open microchannels. The sintering behavior and depth induced by two different sources of the particle-destabilizing chloride, and the resulting conductivity relative to bulk silver is studied. As an alternative printing technique, micron-sized Ag dots are repetitively printed with a hydrogel stamping system on an elastomeric substrate. The height and shape distribution of the printed silver dots, and the origin of defects is discussed. The thesis is concluded by a summary and outlook, in which future prospects of this work in the field of flexible electronics are discussed.

#### References

- [1] B. Geffroy, P. le Roy, C. Prat, *Polym. Int.* **2006**, *55*, 572-582.

- [2] Sony, Rollable OTFT-driven OLED Display, **2010**, http://www.sony.net/SonyInfo/News/Press/201005/10-070E/.

- [3] M. Katsuhara, I. Yagi, A. Yumoto, M. Noda, N. Hirai, R. Yasuda, T. Moriwaki, S. Ushikura, A. Imaoka, T. Urabe, K. Nomoto, *J. Soc. Inf. Display* **2010**, *18*, 399-404.

- [4] P. F. Baude, D. A. Ender, M. A. Haase, T. W. Kelley, D. V. Muyres, S. D. Theiss, *Appl. Phys. Lett.* **2003**, *82*, 3964-3966.

- [5] V. Subramanian, P. C. Chang, J. B. Lee, S. E. Molesa, S. K. Volkman, *IEEE Trans. Compon. Packag. Technol.* **2005**, *28*, 742-747.

- [6] T. Kietzke, Adv. Opt. Electron. 2007, 40285.

- [7] F. C. Krebs, J. Fyenbo, M. Jorgensen, J. Mater. Chem. 2010, 20, 8994-9001.

- [8] R. Søndergaard, M. Hösel, D. Angmo, T. T. Larsen-Olsen, F. C. Krebs, *Mater. Today* **2012**, *15*, 36-49.

- [9] A. Sazonov, D. Striakhilev, C. H. Lee, A. Nathan, *Proc. IEEE* **2005**, *93*, 1420-1428.

- [10] M. Cecchini, F. Signori, P. Pingue, S. Bronco, F. Ciardelli, F. Beltram, *Langmuir* **2008**, *24* 12581–12586.

- [11] S. Li, W. Chen, D. Chu, S. Roy, Adv. Mater. **2011**, 23, 4107-4110.

- [12] U. Palfinger, C. Auner, H. Gold, A. Haase, J. Kraxner, T. Haber, M. Sezen, W. Grogger, G. Domann, G. Jakopic, J. R. Krenn, B. Stadlober, *Adv. Mater.* **2010**, *22*, 5115-5119.

- [13] W. B. Jackson, H.-J. Kim, O. Kwon, B. Yeh, R. Hoffman, D. Mourey, T. Koch, C. Taussig, R. Elder, A. Jeans, *Proc. SPIE* **2011**, *7956*, 795604.

- [14] M. D. Dickey, K. J. Russell, D. J. Lipomi, V. Narayanamurti, G. M. Whitesides, *Small* **2010**, *6*, 2050-2057.

#### Chapter 2

### High-Resolution Patterning Strategies for Flexible Electronics

In this chapter, the development of conventional mass-printing strategies into high-resolution, alternative patterning techniques is reviewed with a focus on large-area patterning on flexible substrates. In the first part, conventional and digital printing techniques are introduced and categorized. The limitations of conventional printing guides the reader to the second part of the review, describing alternative lithographic strategies for patterning on flexible foils for the fabrication of flexible electronics. Soft and nanoimprint lithography-based patterning techniques and their limitations are surveyed with respect to patterning devices on flexible foils. These device structures show a shift from fabricating simple microlense structures to more complicated, high-resolution electronic devices. The development of alternative, low-temperature processable materials and the introduction of high-resolution patterning strategies will lead to the low-cost, self-aligned fabrication of flexible displays and solar cells from cheaper but better performing organic materials.

#### 2.1 Introduction

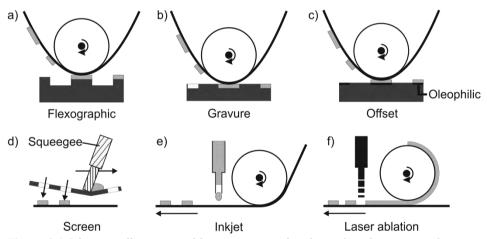

With the invention of the first European movable type printing around 1440 by the goldsmith Johannes Gensfleisch zum Gutenberg, economical and multiple production of alphabet communication became feasible. [1] Knowledge spread rapidly and literacy increased as a result of typography. One of the first books widely spread across Europe was the Gutenberg Bible around 1450. Today, practically all movable type printing ultimately derives from Gutenberg's movable type printing, which is often regarded as the most important invention of the second millennium. Four conventional printing techniques exist, named after the type of master used for printing: relief printing (flexographic), intaglio printing (gravure), planographic printing (offset), and print through (screen printing) (Figure 2.1a-d). [2] Next to the conventional printing techniques, also two digital printing types are shown: inkjet printing and laser ablation (Figure 2.1e-f).

**Figure 2.1** Schematic illustration of four conventional and two digital printing techniques. The techniques can be categorized into (a-d) impact and (e-f) non-impact printing, and furthermore in (a-e) additive and (f) subtractive patterning. Illustrations are based on [2].

In flexographic printing, the ink is transferred from the protruding elements of the printing master to the substrate. In gravure printing the opposite occurs: the relatively low viscous ink is transferred from the pits of the master to the substrate. In offset, images are formed by the physicochemical difference between oleophobic and oleophilic areas on the

printing master, thus eliminating the need for a pattern relief. In screen printing, the color is pressed though a mesh onto the substrate. All four conventional printing techniques apply pressure to the substrate during ink transfer. In digital printing forms such as inkjet and aerosol jet (Figure 2.1e), a pattern is made from a digital image without applying pressure to the substrate. It is thus a non-impact technique. The ink is dropped from a nozzle onto the substrate. In the presented printing techniques, ink is deposited onto the substrate. Laser ablation (Figure 2.1f) however, is a subtractive patterning technique. With lasers, thin layers of a donor material can also be transferred, in a process called laser-induced forward transfer (LIFT), from a glass support onto an acceptor substrate (e.g. Si, foil) which is placed in close vicinity. In this process, developed by Bohandy<sup>[3]</sup> in 1986, a pulsed laser beam heats and melts for example a metal through the glass support. Upon sufficient heating, mainly glass components[4] are turned into their gaseous state at the glass/metal interface, building up high pressures that blast metal off the glass support. Metals,[3-5] liquids,[6-7] and organic materials[5, 8] have been transferred onto acceptor substrates with a highest resolution of 30 µm<sup>[5]</sup> to fabricate OTFTs on Si,[5] and polymer light-emitting diodes (PLEDs) on glass.[8] Flexible OLEDs and OFETs have been reported with a slightly altered LIFT process.[9] Direct laser damage of sensitive materials, such as organic dyes or semiconductive polymers, can be avoided by addition of a dynamic release layer (DLR), converting light to heat by thermal evaporation or chemical decomposition.[8] The absence of a printing master makes digital printing (incl. LIFT) more customizable and results in less waste with respect to chemicals and target material. Utilization of a digital master has the considerable advantage of reduced cost, as the cost and complexity of producing a master range from relatively low cost in the case of screen printing to medium cost for flexographic printing and very high cost for gravure printing.[10]

The area of printing continued to develop and expand from printed text on paper to printed electronics on other materials such as textiles and polymeric foils. Semiconductor research and the invention of the pointcontact transistor at Bell laboratories in 1947<sup>[11]</sup> by Bardeen, Brattain and Shockley was followed up by the invention of the first silicon transistor<sup>[12]</sup> by Texas Instruments in 1954 and the first metal-oxide-semiconductor field-effect transistor (MOSFET)<sup>[13]</sup> in 1960 again at Bell labs, paying the way to practically all modern electronics. The worlds ever demanding decrease of feature sizes for the fabrication of more densely packed, faster electronic circuits and devices has been described by Gordon Moore in 1965.[14] His law predicts the doubling of the number of transistors that can be placed inexpensively on an integrated circuit approximately every two years. Research and development of tools, allowing reproducible patterning at an ever decreasing scale, are in the focus of the semiconductor manufacturers. Fabrication costs and addition of device functionalities follow thereby Moore's law as a target roadmap. Since all competitors work with the identical development timeline, Moore's law can be viewed as a self-fulfilling prophecy. [15] However, the 2011 annual report of the International Technology Roadmap for Semiconductors maintained the in 2010 predicted slowing growth at the end of 2013.[16] after which time transistor counts and densities are to double only every three years. High-end products with extremely short switching times and high integration densities are made of conventional electronics, fabricated on small areas on rigid substrates with sophisticated, high energy consuming techniques.

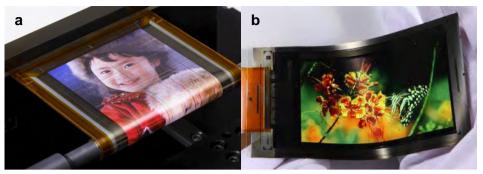

More recently, the area of printed electronics encountered a rapid development towards flexible devices. The motivation for this development can be found in the promise of low-cost, high-volume, high-throughput production in roll-to-roll (R2R) or sheet-to-sheet (S2S) processing lines of electronic components or devices which are light weight and small, thin and flexible, inexpensive and disposable.<sup>[17]</sup> Typically, the aim is to fabricate (semi-) transparent, bendable and even rollable flexible electronic devices such as organic light-emitting diode (OLED)-based displays (Figure 2.2),<sup>[18]</sup> radio frequency identification (RFID) tags,<sup>[19, 20]</sup> and organic solar cells (OSCs).<sup>[21]</sup>

**Figure 2.2** Photographs of rollable AMOLED displays. (a) 4.1 inch OTFT-driven flexible OLED with a total thickness of 80  $\mu$ m, presented by Sony at the SID-2010 in Washington, USA [22]. Reproduced with permission by the Society for Information Display. (b) 3.4 inch flexible AMOLED Display with 326 pixels per inch and a total thickness of 50  $\mu$ m [23]. Copyright © 2011, The Japan Society of Applied Physics.

A key requirement for flexible displays and flexible complementary metal-oxide-semiconductor (CMOS) devices is the low temperature fabrication of organic thin-film transistors (OTFTs) on flexible substrates.<sup>[24]</sup> Flexible electronics face new challenges, not necessarily originating from the small dimensions of the device, but from the deformations and dimensional instability of the substrate.<sup>[25]</sup>

In the first part of this chapter, the history of mass-printing techniques is reviewed and examples of these printing strategies for the fabrication of flexible electronics are given and discussed. The next part describes the development of photolithography and the bottlenecks of processing on low-cost polymeric substrates. From the class of alternative high-resolution patterning strategies, soft and nanoimprint lithography are introduced and their applicability for the fabrication of flexible electronics discussed and reviewed.

#### 2.2 Conventional Mass-Printing Techniques

#### 2.2.1 Flexographic Printing

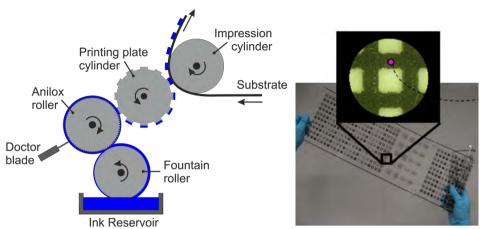

Flexographic printing (Figure 2.3) is a relief printing technique very similar to letterpress. The image is printed from protruding elements on a plate cylinder, transferring the image to almost any type of substrate including plastic, metallic films, cellophane, and paper. The elastic printing plate is made by exposure of a light-sensitive polymer, by computer-guided laser engraving, or through a molding process from a metallic plate creating a 3D relief in a rubber or polymer material. Every color has its own printing plate. Therefore, a multicolor picture requires mounting marks to ensure an exact build-up of the different elements of the picture. As mounting marks, microdots (down to 0.3 mm) and/or mounting crosses are utilized. Ink is transferred from the ink or fountain roll to an anilox roll, the textures of which hold a specific amount of ink. The amount of ink is controlled by the number of engraved cells (mostly inverted pyramids), ensuring an evenly and quick transfer of a controlled amount of ink with a uniform thickness to the printing plate. The anilox roll is typically made of chromecoated ceramics or stainless steel, and represents the most sensitive part of the flexographic process. The amount of transferred ink critically depends on the quality of the cells. Wear of these cells results in less ink transfer or blurred images. Any excess of ink is removed from the anilox roll by a doctor blade. The reliefs on the printing cylinder pick out ink from the anilox roll (Figure 2.4), whereafter the ink is finally printed by pressing the web substrate against an impression cylinder.

**Figure 2.3** Schematic illustration of flexographic printing, and a photograph of a flexographically printed sacrificial black ink on PEN foil [26]. Copyright © 2010 IEEE.

**Figure 2.4** Photograph of (a) an anilox roller after ink pick out from the printing cylinder. (b) The printing cylinder with a silver paste-inked relief during printing. The final printed pattern on the foil can be observed in the background. Reprinted from [27], Copyright © 2012, with permission from Elsevier.

Three line-ups of flexographic printing are known. In *stack press*, the color stations are stacked up vertically, allowing easy access and printing on both sides of the substrate. A good registration is obtained in *common impression press*, allocating all color stations in a circle around the impression cylinder. With *in-line press* heavier substrates, such as corrugated boards, can be printed by horizontally placed color stations. Next to the wide variety of substrates, a typical advantage of flexography is the wide range of inks that can be printed: solvent-based inks, water-based inks, electron-beam curing inks, UV curing inks and two-part chemically-curing inks (usually based on polyurethane isocyanate reactions).

With flexography, continuous conductive grids of Ag ink have been reported on indium tin oxide (ITO)-coated poly(ethylene terephthalate) (PET) foil with a minimal line width of 75 µm. [28] The typical resolution limit of  $50-100 \,\mu m^{[29]}$  for flexography can be reduced to  $\sim 20 \,\mu m$  by controlled edge dewetting and film breakup of inks, transferring for example Ag ink from a poly(dimethyl siloxane) (PDMS) mold to SU8-coated substrates.[30] In combination with slot-die coating, n-octanol has been flexographically printed on poly(3-hexylthiophene): phenyl-C61-butyric acid methyl ester (P3HT:PCBM) to enhance the wettability for the following slot-die coated poly(3,4-ethylenedioxythiophene) - poly(styrene sulfonate) (PEDOT-PSS) layer for the fabrication of a polymer solar cell on PET foil.[10] With flexography, the dielectric and gate of a top-gate OTFT on PET foil have been printed, being the only mass-printing technique applying a sufficiently low pressure in order to avoid destruction of the underlying layers.[31] A lift-off process was introduced for the fabrication of the lower electrode of a microelectromechanical system (MEMS)-controlled Fabry-Perot display on poly(ethylene naphthalate) (PEN) foil, patterning a 2 µm thin sacrificial layer of black ink by flexography at 5 m/min (Figure 2.3).[26, 32]

Flexographic printing is designed for thin, uniform layers providing a better pattern integrity and sharper pattern edges than gravure printing. [26] It is characterized by a continuous reproduction of images or patterns on basically all types of substrates, including flexible foils and corrugated boards. Flexographic printing is less destructive than other mass-printing techniques, applying only low pressures to pre-patterned structures on the substrate. [31] In flexography, the formation of continuous, arbitrarily oriented, uniform lines does not rely on merging of discrete dots, which is different for screen, gravure and inkjet printing. The lack of a continuous line in the other three printing techniques, particularly for fine features, has a negative effect on the line consistency, caused by defects such as pinholes, blocked cells and missing dots. [28] Flexographic printing of a liquid-phase ink material is prone to film instability and dewetting, thereby forming many defects such as open lines. [30] With flexography, only thin

layers can be printed, while gravure printing allows control over the feature thickness by adjusting the cell depth.

#### 2.2.2 Gravure Printing

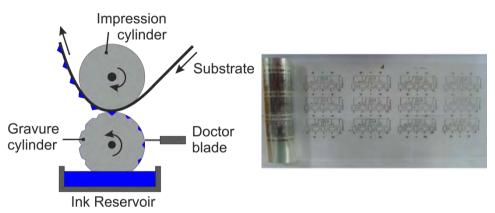

In gravure (intaglio) printing, an engraved cylinder is rolled over a moving substrate, typically paper or plastic (Figure 2.5). [33] Excess of ink is removed from the protruding elements of the cylinder by a doctor blade before the relatively low-viscosity ink is transferred from the cells to the substrate. Typical cell densities are between 220 and 400 cells per inch, with a groove or cell depth  $\sim$ 40 µm and width <100 µm. [34]

**Figure 2.5** Schematic illustration of gravure printing, and a photograph of R2R-gravure printed Ag-ink on PET [35]. Copyright © 2010 IEEE.

In daily life, rotogravure printed products can be found in the form of magazines, catalogues, packaging, decorative papers, etc. The width and thickness of printed dots depend on the cell emptying [34, 36] and drop spreading behavior, being a function of the depth and width of the engravings in the mold, [37] print speed, ink viscosity and the ink/substrate surface energies. [33] Uniform lines can be formed by merging droplets at a cell spacing to cell width ratio of 1.06 up to 1.40. At a ratio larger than 1.40, scalloped lines will be produced. Downscaling is believed to be possible with adjusted ink formulations. A study on overlay printing registration accuracy [35] showed a deficiency of 40  $\mu$ m with a maximum of 59  $\mu$ m parallel to the web moving direction and 16  $\mu$ m with a maximum of 29  $\mu$ m

in the perpendicular direction. The main reason for the attained large value is given by the variability in the web tension, vibration and thermal expansion of the gravure machine, and the thermal expansion of the PET substrate by Ag sintering at <150°C. A combination of rotogravure and inkjet printing has been utilized to fabricate top and bottom gate TFTs on PEN foil.[38] Gravure printing was used to print 70 nm thick, 20-21 µm wide Ag lines (rms roughness 5.8 nm), a 100 nm thin dielectric and the semiconductor. The top electrode was patterned by inkiet printing for precise alignment with a novel fluid guiding technique, resulting in an overlap with the gate and <20 μm line spacing. All-gravure printed OTFTs on PET foil with single-walled carbon nanotubes (SWNT) as semiconducting layer have been reported, studying the overlay printing registration accuracy (OPRA) and line edge roughness of the source-drain electrodes.[39] Bottom-gate TFTs with a channel length of 170 µm, a width of 3000  $\mu$ m, a thickness of 680 nm, OPRA of  $\pm 10~\mu$ m, and a surface roughness of 200 nm have been obtained. Gravure printing has also been used to pattern SiO<sub>2</sub> isolation and spacer structures of a MEMS-controlled display on PEN foil<sup>[26]</sup> and the semiconductor and dielectric of a ring oscillator on PET foil.[40] An optimized gravure plate design, containing the mesh, cell size, cell density, cell depth and cell angle was used to control the thickness of the SiO<sub>2</sub> to print three primary colors red, green and blue.

In summary, gravure printing is a mechanically simple process with fewer controlling variables when compared to competing high-speed printing processes such as flexography or offset lithography. It is known to be advantageous for its high-throughput, high-quality printing of half-tone images, and printability on different materials.<sup>[41]</sup> Gravure-printed layers are adjustable by the cylinder's cup design<sup>[26]</sup> (e.g. depth of cell), allowing thick layers to be printed on flexible substrates. Gravure printing requires a precise adjustment of each ink formulation regarding its viscosity and surface energy,<sup>[42]</sup> allowing also printing of low viscosity inks (e.g. semiconductor inks)<sup>[31]</sup> which cannot be handled by the other mass printing techniques. Furthermore, the fabrication of the gravure plate is more expensive compared to other printing techniques.<sup>[10]</sup>

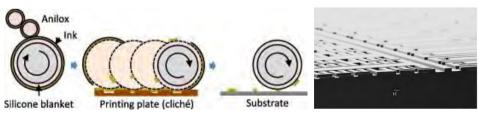

#### 2.2.3 Offset Printing

In offset lithography (Figure 2.1c), introduced at the end of the  $18^{\rm th}$  century by Alois Senefelder, [2] images are formed by the physicochemical difference between oleophobic and oleophilic areas on the printing master, thus not requiring a pattern relief. The main carrier is oleophobic and often made of aluminum, while the color is taken up mostly by an oleophilic grease layer. Offset-printed features have typically a resolution in the range of 20  $\mu m$  and a layer thickness below 1  $\mu m$ , [43] allowing microstructuring up to 200 000 m²/h. Offset-printed top gate TFTs have been reported on PET foil, showing a gap width in the range of 50  $\mu m$  and a linewidth down to 100  $\mu m$ . The dry layer thickness obtained for printed PEDOT was 600 nm. [43]

A modified offset printing technique<sup>[44]</sup> (Figure 2.6) has been developed by LG Display Co., printing thin and uniform layers of etch resist to form fine patterns of  $10 \mu m$  width and  $6 \mu m$  spacing as short channels of a TFT on Si. In the modification, an ink-coated roll blanket with low surface energy is pressed against a patterned printing plate (Figure 2.6) with high surface energy. Undesired ink is transferred to the printing plate, leaving the desired patterns on the roll blanket. The patterns are printed in the subsequent step from the blanket onto the substrate by rolling.

**Figure 2.6** Schematic illustration of modified offset printing and scanning electron microscopy image of the Si printing plate. Reprinted from [44], Copyright © 2012, with permission from Elsevier.

Offset printing is, in summary, an attractive patterning strategy for the source and drain patterning of top-gate OTFTs. The printing plate fabrication is comparatively simple and inexpensive.<sup>[31]</sup> At the same time it shares the high resolution and layer quality of gravure printing. On the

other hand, the layer thickness resulting from offset-printed features is reported to be more inhomogeneous showing a higher surface and edge roughness when compared to other mass-printing techniques. In a given example, [31] the average layer thickness was 600 nm with observed local layer thicknesses from 50 nm to 3  $\mu$ m on PET foil.

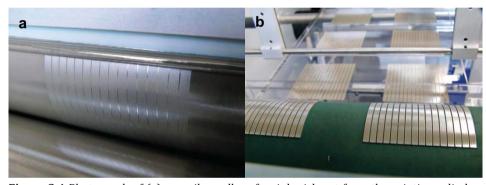

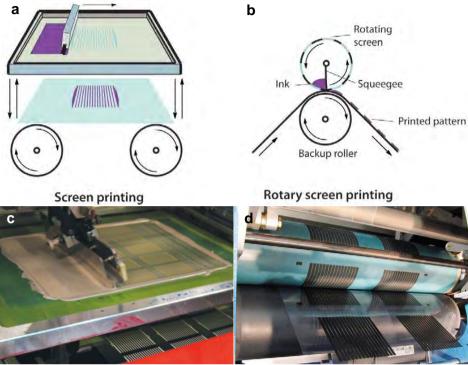

#### 2.2.4 Screen Printing

In screen printing, [45] ink is pressed with a squeegee through a screen onto the substrate. The screen is made of a porous mesh, from materials such as a porous fabric or stainless steel, stretched tightly over a frame made of wood or metal. Proper tension is essential for accurate color registration. The image to be replicated, the stencil, can be photochemically or manually defined on the mesh. The squeegee is typically made of a rubber, and is therefore prone to wear. Due to the simplicity of the process, a wide variety of substrates and inks can be used, allowing a high layer thickness which is typical for screen printing. From the three types of screen printing, rotary *screen printing* (Figure 2.7b, d) has the highest throughput, edge definition/ resolution and achievable wet thickness.<sup>[27]</sup> In the other two techniques, flat-bed (Figure 2.7a, c) and cylinder, a flat screen is pressed against a substrate. In flat-bed, the substrate is positioned horizontally parallel to the screen, while in cylinder press the substrate is mounted on a cylinder. Screens for rotary screen printing are seamless thin metal cylinders. The squeegee in rotary screen printing is fixed in the cylinder (Figure 2.7b),[27] or it is a free floating steel bar inside the cylinder with a magnetic pressure control.<sup>[45]</sup> Rotary screen presses are most often used for printing textiles, wallpaper, and other products requiring seamless continuous patterns.

**Figure 2.7** Schematic illustration and photograph of (a, c) flat-bed and (b, d) rotary screen printing. (c) Flat-bed screen printing of silver paste showing how the squeegee forces the ink through the screen onto the underlying foil. (d) Rotary screen printing of conducting graphite ink onto a clear polyester foil. Reprinted from [27], Copyright © 2012, with permission from Elsevier.

In industrial processes, screen-printed films usually have a thickness larger than  $\sim\!0.5~\mu\text{m.}^{[46]}$  Thin and homogeneous layers are not easily obtained by screen printing. As an example, the inhomogeneous 100 nm hole transport layer of an OLED has been reported. [47] Nevertheless, also a 40 nm thin active layer of a bulk hetero-junction photovoltaic device with an rms value of 2.6 nm has been reported. [46] Both devices have been fabricated on glass substrates. Silk screen-printed polymer solar cells have been reported on PET foil by Krebs et al.. [48] The anode pattern was defined into an ITO-coated PET foil by rotary screen printing an etch resist and subsequent etching. Electrical contacts made of epoxy silver paste and the conjugated polymer were also screen printed. A screen with a thread diameter of 27  $\mu$ m and a mesh count in the range of 140-220 cm-1 was used. Flexible

pentacene transistors have been demonstrated<sup>[49]</sup> with room temperature, silk screen printed silver resist, forming the top contact source-drain electrodes on poly(phthalate carbonate) foil. The channel length was varied from 40  $\mu$ m to 200  $\mu$ m at a fixed channel width of 1.5 mm. CMOS devices on PEN foil<sup>[50]</sup> have been fabricated by laser ablation of a 30 nm gold source-drain layer and screen printing. The p- and n-type semiconductor, a 800 nm-thick dielectric fluoropolymer and a gate layer of silver paste were subsequently screen printed, showing a process alignment of  $\pm$  25  $\mu$ m for all printed materials. With the printed inverters, a voltage-controlled oscillator and two differential organic amplifiers were presented. Very recently, a solely screen-printed device, a flexible thin film supercapacitor on polyester (PE) foil, has been reported. [51]

Screen printing is an inexpensive, large-area printing technique with good control over the deposition area. This is important, for instance, for fabricating a device that is integrated onto a substrate containing other electronic devices. The quality of screen-printed films depends highly on: the number of fibers in the screen mesh, the tension of the mask, the distance from the mask to the substrate, the characteristics (hardness, edge) and process parameters (speed, pressure, angle) of the squeegee, the temperature, the humidity and the air flow around the printing area.<sup>[52]</sup> The ink viscosity is linked to all parameters mentioned, and has to be critically adjusted to match the mesh used in the screen mask such that the polymer solution will not run through the mask but will be transferred through the mesh upon application of mechanical pressure.<sup>[48]</sup>

#### 2.2.5 Inkjet Printing

A printing technique in the field of organic, large-area electronics often combined with the above reviewed mass-printing techniques is the additive, direct patterning technique of inkjet printing. Therefore, it will be discussed in this section. Precise quantities of a wide range of materials can be deposited in the form of conducting lines or single droplets on various substrates (e.g. foils). It is a low-cost, non-impact and rapid technique with

a large potential to manufacture electronic circuits. Costs are reduced owing to digital imaging, eliminating the multiple process steps involved in using a photolithographically defined etch mask and the subsequent deposition and etching steps. As inkjet printing is a relatively fast technique, it potentially enables fast R2R patterning of conductive precursor materials,<sup>[53]</sup> such as metal nanoparticles<sup>[54, 55]</sup> or metal–organic complexes.<sup>[56]</sup>

The key challenge is developing suitable ink formulations, determining the drop ejection characteristics and dictating the quality of the printed electrocircuits by influencing the evaporation behavior and orientation (e.g. crystal orientation) upon solvent evaporation. Clogging of nozzles is a serious issue of inkjet printing and can reduce the yield substantially. The resolution is limited to 20 to 50 µm by statistical variations of the flight direction of droplets and their spreading on the substrate.<sup>[57]</sup> Especially in metal conductive inks, uniform and monodisperse metal nanoparticles in aqueous or organic solvent dispersions[58] contribute to attain a high dispersion stability and low electrical resistivity at low metallization temperatures.<sup>[54]</sup> The typical sintering step needed to render the precursor compound conductive, requires >30 min process time and/or higher temperatures (>250°C).[53] High sintering temperatures are incompatible with common polymer foils, such as PET and polycarbonate (PC), having a relatively low glass transition temperature. The choice of foil is therefore restricted to more expensive polymers such as polyimides (PI).[53]

Among the inkjet-printed metal conductive inks, Ag formulations receive a lot of attention, [58] and the first Ag inks are commercially available (e.g. BayInk® nanoparticulate silver inks, *Bayer Material Science*). A second type of Ag ink is known as a metal-organic decomposition (MOD) ink. Typically, heat is required to precipitate the metal and burn off the organic ligand in MOD inks, or, in case of NP inks, decompose the organic stabilizer. [53] Reported room temperature sintering techniques destabilize the metal inks by slow evaporation of the solvent or in a faster approach by chemical destabilization. As an example, the coalescence of Ag NPs by exposure to

HCl vapor has been reported (see also Chapter 7 in this thesis). [58, 59] Inkjet printing of seeding particles for subsequent electroless deposition of metals is another R2R-compatible route to metal lines. [60] Inkjet-printed, conjugated polymers have been reported in LEDs and, in combination with photolithographic patterning of hydrophilic and hydrophobic areas, TFTs on glass. [57] Fully inkjet-printed TFTs have been reported that were fabricated through patterning and sintering each individual layer of the device at an annealing temperature <150°C (compatible to PET) allowing the formation of conductive lines. [60] Recently, [61] self-aligned fully printed TFTs on PET foil with a minimal gate to source-drain overlap of 0.47  $\mu$ m have been reported. In this case, self-alignment was obtained by wetting-based roll-off techniques of the droplets from previously patterned layers.

In summary, inkjet printing is a versatile, non-contact patterning technique with a resolution down to 20  $\mu m$ . It is a fast technique often combined with other patterning strategies. Examples of combinations with mass-printing techniques have been given in the previous sections. Combination with high-resolution patterning strategies will be given in the following sections. Furthermore, digital mastering reduces processing costs and allows fast changes to the design.  $[^{10]}$  Drawbacks of the technique are the necessary adjustment of the ink viscosity, concentration and solvent system to the nozzle (to prevent clogging) and the substrate material. Spreading of the ink and wanted or unwanted merging of dispensed droplets needs to be controlled. Further fine-tuning of solvent, concentration and viscosity is required to control the shape, thickness and morphology of the evaporated droplet.

#### 2.3 High-Resolution Patterning

With conventional printing techniques, only a resolution of around 10  $\mu m$  can be obtained, limiting the bandwidth to 10 kHz for printable semiconductors with a typical mobility of  $0.01~cm^2V^{-1}s^{-1}$ . Advanced and flexible electronic devices demand high-resolution patterning techniques.

When taking OTFTs as an example, high-resolution patterning would result in a larger bandwidth and higher switching speed while the geometric (parasitic) capacitance, the operation voltage and power consumption will be reduced. In addition, an improved on/off ratio at lower costs with a higher yield on smaller areas is possible.

In general, two types of high-resolution patterning techniques can be distinguished: top-down and bottom-up. In top-down, various lithography methods are miniaturized to pattern nano- to micronscale patterns. Photolithography and scanning beam (or maskless) lithography (e.g. electron beam and focused ion beam lithography) are the main patterning techniques in this area. The most known and widely spread patterning technique in semiconductor industry is optical lithography, which is therefore the only technique that will be covered in the following sections.

#### 2.3.1 Photolithography

Photolithography (and its descendants) is the main patterning technique of the semiconductor industry. It proved to be far more capable of reducing the minimal feature dimensions to fulfill Moore's law than one could have imagined. In the 1960s through the mid-1980s, mercury lamps were utilized as light source, producing light across a broad spectrum with several strong peaks at 436 nm ("g-line"), 405 nm ("h-line") and 365 nm ("i-line"). Light filters allowed specific selection of the required spectral line to ideally match to the photoresist. The request of the semiconductor industry for denser and faster chips was met by the development of excimer laser lithography in 1982 by Kanti Jain<sup>[63, 64]</sup> at IBM, leading in the end to the steppers and scanners as primary patterning tools used in microelectronics production of today's world. Today, the world's leading provider of lithography systems for the semiconductor industry ASML, has started commercializing their pre-production, extreme ultraviolet lithography tool NXE:3100.<sup>[65]</sup> The tool is based on 13.5 nm wavelength

technology, patterning according to their roadmap at a resolution of 16 nm.<sup>[66]</sup>

In the following lines, the basic principle, developments and limitations of photolithography are described. Thereafter, the main challenges of transferring this technology and derivatives to flexible foil will be discussed.

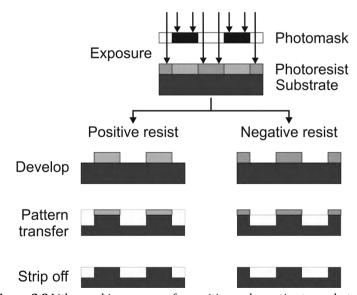

In photolithography, patterns are made by exposure of a thin layer of a photosensitive lacquer (i.e. photoresist) on a substrate through a mask. The photomask is usually made of glass and a thin, light-blocking layer, typically made of chromium. Light exposure induces a chemical change of the light-sensitive material, changing its solubility in a developer solution. For positive tone resists the exposed, and for negative tone resists the unexposed regions are removed upon developing, resulting in a three-dimensional replica or inverted replica of the photomask on the substrate. The patterned photomask can be used in a subsequent process step as etch mask in order to define features on the wafer (Figure 2.8).

Figure 2.8 Lithographic processes for positive and negative tone photoresists.

Photolithography has a couple of limitations. The minimal resolution R (i.e., critical dimension CD), given by the Rayleigh equation (equation 2.1), is

diffraction limited to the wavelength  $\lambda_{\theta}$  in vacuum of the irradiating visible or UV light by the Rayleigh coefficient of resolution  $\kappa_{1}$  and the refractive index n of the incident medium, divided by the angular aperture  $\theta$  of the lens system. The product  $n \cdot \sin \theta$  is also known as the numerical aperture (NA) of the imaging system. The factor  $\kappa_{1}$  is a process-dependent parameter that is determined by illumination conditions, mask technology, and photoresist capabilities with a lower limit of 0.25 for single-exposure optical lithography. [67]

$$R = \frac{\kappa_1 \lambda_0}{n \cdot \sin \theta} \tag{2.1}$$

The resolution limit of optical lithography has been continuously improved by reducing the exposure wavelength and increase of the numerical aperture. High-end optical lithographic patterning techniques such as deep- and extreme UV,<sup>[68]</sup> X-ray<sup>[69]</sup> and immersion lithography<sup>[67, 70]</sup> have pushed the resolution limit into the sub-micrometer and tens of nm regime on Si substrates.

On flexible substrates, photolithography is often used to pattern large micrometer features such as a gate or source-drain terminals,[71,72] but also the semiconductor is regularly patterned by photolithography.[73] Flexible, all-polymer FETs have been fabricated by exposing a conducting polymer mixed with a photoinitiator through a photomask with deep UV radiation, rendering the exposed polymer non-conductive.[74]

#### 2.3.2 Towards Alternative Methods for High-Resolution Patterning

Photolithographic processing requires many steps, is subtractive, and only suitable for patterning small areas.<sup>[75]</sup> The substrates and organic electronic materials are exposed to corrosive etchants, high-energy radiation, and relatively high temperatures during processing. The high investment and operation costs of photolithographic processing at the

resolution limit, are feasible as long as high yields and volumes are targeted. An economically more feasible route to high-resolution electronic devices is envisioned by one of the next-generation lithography techniques (e.g. nanoimprint lithography) on low-cost, polymeric foils. These alternative, high-resolution patterning techniques can be operated at lower costs to obtain the same or an improved resolution compared to the highend photolithography systems. The integration in high-throughput patterning facilities such as a R2R line, would allow the fabrication of low-cost, large-area, flexible and lightweight devices. However, the transfer of processes from Si to polymeric foils is challenging and not straightforward.

Flexible electronic materials and interconnects offer thinner, lighter, highly compact end-products, and, often, a better performance.<sup>[76]</sup> Thin-film polymeric foils with a typical thickness of 25–200 µm are made of polyester (PE), polyimide (PI) or polycarbonate (PC).[77, 78] PE, and then mainly PET and PEN, are often used<sup>[79-81]</sup> and well-studied,<sup>[82, 83]</sup> showing a reasonable good mechanical stability and resistance to oxygen and water vapor penetration. Protection of the mainly organic materials of the electronic device from moisture and oxidation can be enhanced by barrier layers, additionally deposited on the foil. Barrier layers can also increase the chemical resistance of the polymers. The most stringent restriction to the patterning process and materials is the limited temperature window. The low glass transition temperature of the polymeric foils (e.g. ~70-85°C for PET<sup>[84]</sup>) requires alternative deposition techniques and newly engineered materials. As examples of recently developed, low-temperature materials, a high-k dielectric from titanium dioxide[85] and highly conductive selfsintering silver nanoparticles<sup>[58]</sup> have been reported. The second effect of temperature elevation on the polymeric substrates is a reduced dimensional stability due to a high coefficient of thermal expansion, even for biaxially oriented and thermally stabilized foils.[86] The dimensional stability and waviness of the foils can be improved by a bond-debond approach, temporarily laminating and flattening the foil to a carrier (e.g. Si or glass). These foil-on-carriers (FOCs) supply a stable platform for foil processing, but many new variables are introduced (e.g. bowing) and need to be studied and tuned.<sup>[25, 86-90]</sup> Other bonding strategies developed are Electronics-on-Plastic by Laser Release (EPLaR) by Philips Research,<sup>[91]</sup> and Flexible Universal Plane for Display (FlexUPD) by ITRI.<sup>[92]</sup> In EPLaR, PI is coated on display glass as used in TFT-LCD processing plants. A regular TFT matrix is formed on top of it, whereafter the flexible display is released using a laser, allowing also reuse of the glass. In FlexUPD, PI is deposited on glass substrates with local debonding areas. A device (e.g. AMOLED) is patterned over the debonding area, allowing simple and quick cut-out of the patterned device with a slot die coater. The glass carrier cannot be reused however. For mass production, a prototype of an automated flexible-substrate debonding apparatus facilitated with a vacuum system has been reported by ITRI.

The limitations of conventional patterning resulted in the development of new or "alternative" nanopatterning strategies. Amongst these are soft lithography and nanoimprint lithography (hot embossing and UV NIL).

#### 2.4 Soft Lithography

Soft lithography<sup>[93, 94]</sup> is a collective term for a set of techniques to pattern substrates from the micro- to nanoscale using an elastomeric stamp or mold,<sup>[93]</sup> typically made of PDMS. A variety of techniques has been developed and named after the utilization of the soft mold. In soft lithography, patterns are formed by printing inks, embossing microstructures, and replica molding by any of the following techniques:

- Microcontact printing (μCP)<sup>[95]</sup>

- Micromolding in capillaries (MIMIC)[96]

- Nanotransfer printing (nTP)[97-99]

- Replica molding (REM)<sup>[100]</sup>

- Microtransfer molding (μTM)<sup>[101]</sup>

- Solvent-assisted micromolding (SAMIM)[102]

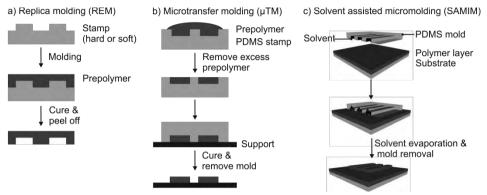

Only the main soft-lithographic techniques ( $\mu$ CP, MIMIC, and nTP) utilized to pattern electronic devices on flexible foils will be further introduced and the obtained results discussed in the following sections. To complete the overview, the basic principles of the non-discussed soft lithographic patterning techniques REM,  $\mu$ TM and SAMIM are illustrated in Figure 2.9.

**Figure 2.9** Schematic illustration of the soft lithographic patterning techniques: a) replica molding, b) microtransfer molding, and c) solvent-assisted micromolding.

#### 2.4.1 Microcontact Printing (µCP)

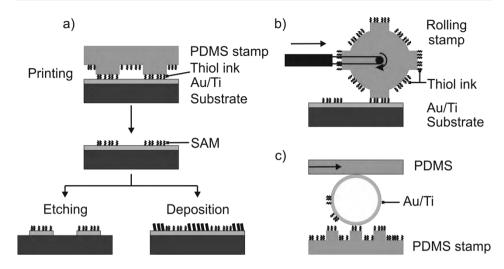

Microcontact printing ( $\mu$ CP) (Figure 2.10) is probably the best known soft-lithographic patterning technique. Invented by Whitesides et al. in the beginning of the 1990s, [103] this remarkably simple patterning technique is employed to form routinely self-assembled monolayers terminated with different chemical functionalities with (sub)micron lateral dimensions. [93] In short, a flexible, elastomeric stamp (typically made of PDMS) with patterned reliefs is inked by an alkanethiol solution. After drying, the stamp is pressed gently against a gold-coated substrate (or other thiol-compatible surface, e.g. silver or copper). Conformal contact between stamp and substrate ensures the transfer of the ink molecules to the substrate, forming rapidly a self-assembled monolayer (SAM) in the contact areas. In a subsequent step, the patterned SAM can be used as etch mask to transfer the pattern into the underlying gold, or a second SAM can be deposited by backfilling.

**Figure 2.10** Schematic illustration of various  $\mu$ CP processes, transferring an alkanethiol to a gold substrate by (a) single printing with a PDMS stamp, (b) continuous printing with a PDMS roller stamp, and (c) printing on a nonplanar surface. Images based on [93].

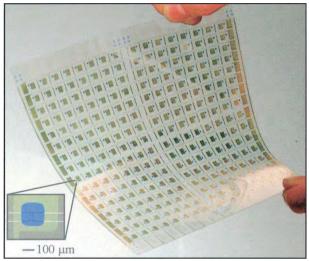

μCP is not restricted to the transfer of thiols to gold. Silanes, organic or inorganic species, biomolecules, and all sorts of materials can be transferred as inks.[104] As an example of alternative inks in the area of flexible electronics, the printing of Al-porphyrin SAMs on carboxylic groups formed on plastic foils (PET, PEN, PI) upon oxidation and on inert polymers (i.e. PE, polypropylene (PP) and poly(tetrafluoroethylene) (PTFE)) has been reported.[105] The patterned Al-porphyrin was used in a subsequent step to selectively deposit palladium-tin colloids, initiating Cu growth by electroless deposition (ELD). Also other SAMs have been printed on PET foil to induce Cu growth by ELD, resulting in Cu wires with a resolution of 0.45 to  $10 \ \mu m.^{[106, \, 107]}$  Microcontact printed SAMs can also be used to induce a wetting/dewetting contrast on a substrate for selective deposition of a sacrificial resist layer in a lift-off procedure to pattern metals.[108, 109] In a wetting-controlled, parallel, low-temperature process, although only demonstrated on Si wafer, µCP was used to pattern a "molecular template" on the substrate directing thin films by spincoating into the desired pattern to fabricate TFTs.[110] Contact printed, organic active matrix backplanes on 5 x 5-inch PET sheets, [111] with 10  $\mu m$  wide and 20  $\mu m$ -spaced source and drain electrodes forming bottom-contact transistors, have been demonstrated as well (Figure 2.11).

**Figure 2.11** Image of a completed plastic active matrix backplane circuit, patterned by  $\mu CP$ . The inset shows an optical microscopy image of a typical transistor [111]. Copyright © 2001 National Academy of Sciences, U.S.A.

#### 2.4.2 Micromolding in Capillaries (MIMIC)

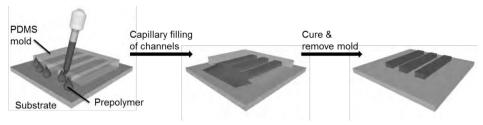

In micromolding in capillaries (MIMIC) (Figure 2.12), first reported by Whitesides et al. in 1995,<sup>[96]</sup> capillaries are formed by placing a soft elastomeric stamp, usually made of PDMS, with parallel protrusions on a smooth surface. The grooves form channels (capillaries), which are spontaneously filled with a solution as an effect of capillary pressure upon placement of a drop of the solution at the open end of the capillary. The filling speed is proportional to the cross-sectional dimensions of the channel and inversely proportional to the length of the channel containing the liquid and to the viscosity of the liquid.<sup>[112]</sup> After complete solvent evaporation or, in case of a low-viscosity polymer precursor after crosslinking, the stamp is removed leaving the patterns on the substrate.

Figure 2.12 Schematic illustration of micromolding in capillaries.

Upon gradual solvent evaporation in the channels, a meniscus is formed under the roof of the stamp channels by capillary forces. Depending on the solute concentration, two kinds of patterns can be obtained. In the high concentration regime, the solution reaches supersaturation when the channel is still filled with solution, resulting in deposition of solute on the entire bottom of the channel. In the dilute concentration regime, supersaturation is reached when most of the solvent is evaporated, and the volume of the residual solvent is not enough to completely fill the channel. In this case, the meniscus forms a U-[113] or W-shape[114] in the channel, dragging under capillary force the solute to the edges of the channel, where it accumulates and aggregates thereby forming defects in the stripes or creating split lines.[115] Specific polymers (e.g. polyaniline, polystyrene) can however, at slow solvent evaporation speed at room temperature, replicate the entire mold dimensions even from very low concentrated solutions of ~1%.[116] They need to undergo a transition to a dispersion in the channel from which polymer chains precipitate out as very small particles. The small particles aggregate upon attractive forces into nucleation sites. Particle influx from the larger reservoir at the channel entrance to the nucleation sites is generated to compensate for the loss of solvent upon evaporation. As an example, lines of polyaniline (emeraldine base) with a resolution between 350 nm and 50 µm were formed by MIMIC. After patterning, the emeraldine base was protonated with an acid to the electrically conductive emeraldine salt. With these polyaniline lines, allplastic field-effect transistors (FETs) have been fabricated on PE substrates.[116] Due to the mechanical instability of the soft polymeric stamp, the dimensions of the channels in MIMIC are typically limited to about a few hundred nanometers.[117] A similar process of patterning a

precursor material with MIMIC on a flexible substrate, and transition into a conductive material after stamp removal, has been reported for graphene oxide. With a hard PDMS stamp, centimeter-long and large-area 10  $\mu$ m wide, ultrathin (1-3 nm) microwires of reduced graphene oxide flakes (500 nm to 1.5  $\mu$ m) have been patterned by MIMIC of graphene oxide in aqueous solution on 3-aminopropyltriethoxysilane (APTES)-treated substrates (SiO<sub>2</sub> wafer, quartz, and PET), followed by a chemical reduction with hydrazine vapor. With the resulting microwires, front-gate FETs have been fabricated that have been used for sensing applications. Also free-standing films or polymer networks with a resolution of 1  $\mu$ m can be created by simply dissolving (e.g. dissolving a SiO<sub>2</sub> sacrificial layer with HF), melting or vaporizing the solid support after MIMIC. [96]

## 2.4.3 Micro and Nanotransfer Printing (µTP and nTP)

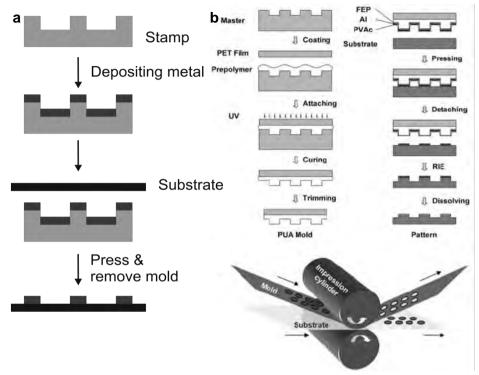

In transfer printing<sup>[97-99]</sup> (Figure 2.13a), a functional layer is picked up by a rigid or elastomeric mold from one substrate and transferred as continuous<sup>[119]</sup> or patterned film<sup>[120, 121]</sup> to a second substrate. The substrate's adhesion energy needs to be carefully selected, allowing pickup of material from the first substrate by the mold and deposition onto the second. The adhesion energies can also be adjusted by chemical functionalization. Depending on the patterning scale, the technique is referred to as micro- or nanotransfer printing ( $\mu$ TP<sup>[122]</sup> or nTP). The feature height of the stamp is in the range of 0.2–10  $\mu$ m, and the width is between 0.05 and 100  $\mu$ m.<sup>[97]</sup>

**Figure 2.13** Schematic illustration of (a) micro- and nanotransfer printing and (b) the fabrication and utilization of a rigiflex mold [123]. Copyright © 2005 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim.

Molds made of UV-curable poly(urethane acrylate) (PUA), so-called rigiflex<sup>[124, 125]</sup> molds (Figure 2.13b), were rigid enough for sub-100 nm patterning<sup>[126]</sup> and yet flexible enough for large-area application in R2R processing. Small molecule and polymer semiconductors for device applications are typically patterned by transfer printing. They are sensitive to oxidation in air and/or show a performance dependence on the polymer microstructure, substrate roughness, film deposition conditions, and solvent exposure.<sup>[121]</sup> The advantage of transfer printing in this case is the absence of process steps that partially can degrade the organic semiconductor or polymer, such as photoirradiation or exposure to incompatible chemicals (e.g. etch solutions), or solvents. Hines et al.<sup>[78, 127, 128]</sup> added the basic concept of NIL<sup>[129, 130]</sup> to nTP, patterning all components (metal, dielectric and semiconductor) of a TFT on plastic substrates (latex, nitrile, polyvinyl chloride (PVC), PET and poly(methylmethacrylate)

(PMMA)). Organic materials allowing processing near or above their glass transition temperature, were successfully transferred by proper adjustment of the heat and pressure during the thermal NIL process. Bottom-contact, bottom-gate TFTs with a PMMA dielectric layer, Au source-drain and gate electrodes and three semiconductor films from different classes (pentacene (small-molecule), P3HT (polymer), and carbon nanotubes (CNT) (macromolecule)) have been patterned on PET foil. John Rogers and coworkers continuously extend the patterning capabilities of nTP. They have reported on patterning of new materials (large-area flexible 3D optical negative index metamaterials<sup>[131]</sup>), and on transferring fully formed MOSFETs with thermally grown gate oxides and constructing integrated circuits to basically any substrate.<sup>[132]</sup>

The strong point of soft lithography is also the technique's weakness. The elastomeric character of PDMS results in stamp deformation upon contacting and during stamp removal. At high aspect ratios, defined as the height divided by the width of the features, buckling or pattern collapse of the elastomeric features can occur owing to gravity, adhesion and capillary forces, [133] generating defects in the pattern to be formed. Low aspect ratios result in sagging as a result of the compressive forces typical of printing and the adhesion between the stamp and the substrate.[93] An aspect ratio between 0.2 and 2 of the relief structures on PDMS surfaces is required to obtain defect-free stamps.[134] Other technical issues for the application of PDMS are the swelling when in contact with nonpolar solvents and the shrinking of about 1% upon curing.[135] An accurate registration for patterning multilayers is also more difficult with a flexible stamp than with a rigid stamp. Next to the general challenges of soft lithography, each technique has its own specific limitations. A drawback in µCP is for example diffusion of the SAM-forming molecules to areas not contacted by the PDMS stamp, broadening the feature itself and blurring the feature edge. With MIMIC, it is difficult to replicate the entire channel in case of a high aspect ratio. Line splitting can occur, breaking up the film in wide channels to result in splitted patterns and a non-flat feature profile. Line splitting can also be willingly used to fabricate thin lines at the channel

sidewalls, but control over the morphology is limited and avoiding line ruptures is a challenge. Furthermore, only low-viscosity inks in structures exhibiting a capillary force can be patterned. Arrays of individual dots for example, do not offer an open side for liquid influx. Nanotransfer printing allows selective transfer of materials to a wide range of substrates, making it a very broadly applicable patterning strategy, especially in combination with rigiflex molds. However, this printing technique requires precise adjustment of the intrinsic surface energies or adjustment by chemical modification or topography, to direct the transfer from the mold to the first or subsequent substrates.

# 2.5 Nanoimprint Lithography

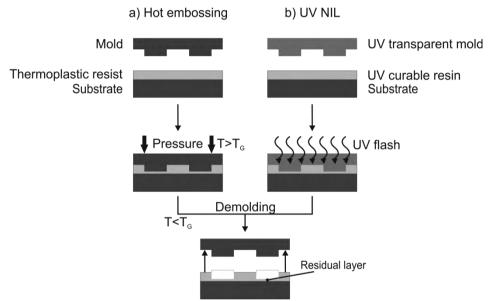

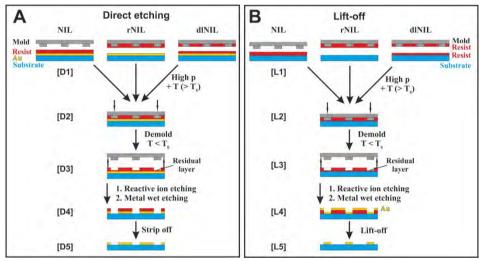

In thermal nanoimprint lithography (NIL) (Figure 2.14a),[136, 137] a technique developed by Chou et al., [129, 130] a rigid mold, typically made of Si, is pressed for a predefined time into an amorphous polymeric resist at a temperature typically 50-70°C<sup>[136]</sup> above the glass transition temperature  $(T_G)$ . The resist suddenly turns low-viscous above  $T_G$  by altering the mechanical and thermodynamic properties of the polymer.[138] The mold protrusions are thereby filled with resist by squeeze flow (pressure is the driving force to displace the viscous resist) and capillary forces (surface energy controls the wetting and spreading of the viscous resist) until it conforms to the surface relief of the mold. [136] Typically, a highly fluorinated SAM (e.g. 1H,1H,2H,2H-perfluorodecyltrichloro-silane)[139] is applied as an anti-sticking layer to facilitate easy demolding and complete transfer of resist. Intrinsically, low-energy molds with high mechanical strength have also been reported, for example made of Teflon AF 2400 (T<sub>6</sub>= 240°C).<sup>[140]</sup> Demolding occurs after reducing the temperature below T<sub>G</sub> and release of pressure. A thin residual layer remains on the imprinted substrate, which is removed by anisotropic reactive ion etching (RIE). The opened windows in the resist layer can be used to etch uncovered parts of an underlying layer (e.g. metal) in a direct etch process. Material (e.g. metal) can also be deposited after residual layer removal, followed by a lift-off step dissolving the resist and the material deposited on top of it. With direct etching, an inverted pattern and with lift-off, a replica of the original mold pattern is obtained. Control over pattern replication and residual layer thickness has been improved by the development of UV-based nanoimprint lithography (UV NIL) in 1996,[141] and the further development into step-and-flash lithography (SFIL) by Wilson et al.,[142] crosslinking a low-viscosity resist by UV irradiation through a fused silica mold (Figure 2.14b). UV NIL allows room temperature imprinting at low pressure with good control over the residual layer thickness, making it (also) an ideal tool for patterning on foil.

**Figure 2.14** Schematic illustration of nanoimprint lithography (NIL) of (a) a thermoplastic resist by hot embossing and (b) a UV curable resin by UV NIL.

NIL has been pointed out as one of the ten next-generation lithography techniques addressing the need for low-cost, high-resolution and high-throughput manufacturing of high-density integrated circuits and optics. In addition to the fabrication of rigid microchips, NIL can also be used as structuring technique in the fabrication of flexible electronic devices. For example, flexible OTFTs with source-drain contacts defined by thermal NIL<sup>[143]</sup> have been reported. Over the past 16 years, a variety of NIL processes has been developed, concerning different types of substrates,

resist materials and molding processes. Semi-continuous and continuous imprinting techniques, such as step-and-repeat imprint lithography (step-and-stamp IL<sup>[144, 145]</sup> for thermal resists, step-and-flash IL<sup>[142]</sup> for UV resists) and R2R NIL<sup>[146]</sup> have been invented for an increased throughput. Nonflat surfaces can be patterned with rigiflex molds<sup>[125]</sup> and reverse NIL (rNIL).<sup>[147, 148]</sup> Small and large features can be patterned by hybrid solutions combining NIL and conventional photolithography (combined nanoimprint- and photolithography; CNP).<sup>[149]</sup>

Complex electronic devices demand a good registration and overlay control in the patterning process. In OTFTs for example, the overlay of the sourcedrain and gate layers is important in order to reduce parasitic effects. Optimal alignment and therefore minimal gate overlap can, especially for R2R processes, only be obtained with a self-aligning patterning strategy. The critical overlay can thereby be obtained by "programming" one of the functional layers (e.g. gate) to define the next layer, or a multilevel etch mask defining all following layers can be fabricated on the substrate. In self-aligned imprint lithography (SAIL),[145-152] the entire material stack is deposited on the flexible foil whereafter a single, three-dimensional imprint is made defining all layers of the electronic device. The individual layers and structures of the device are patterned by smartly switching etch processes, opening one layer after the other using the just opened layer as etch mask and the next layer as etch stop. As an example, individual and arrays of bottom-gate transistors with amorphous silicon and transition metal oxides as active layer have been made on a web of 50 µm thick PI.[150, <sup>153</sup> A UV-curable resist is thereby patterned with a PDMS mold wrapped around a drum replicated from a patterned Si master. Fabricating a PDMS mold from a Si master mold allows numerous replications of the expensive master, without affecting its properties. The fabrication of a multilevel imprint mold in a two-step photolithographic and RIE process for top-gate a-Si TFTs has been reported and demonstrated on Si substrates.[154] Stadlober et al.[62] introduced a self-aligning technique that utilizes a thermal or UV NIL-patterned Al gate as photolithographic mask in a backside exposure step to define the positions of the source and drain in a photoresist. Following shadow evaporation of the source-drain metal, the photoresist remaining exactly above the gate is removed by lift-off. A minimal overlap of 25-30 nm has been obtained.

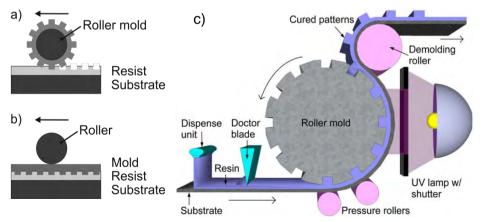

For high-throughput, large-area fabrication of flexible electronics, both sheet-to-sheet (S2S) and R2R NIL (e.g., Roller NIL[155]) configurations seem suitable. An extensive review of continuous roller micro- and nanopatterning has been very recently reported by Dumond,[156] giving a good overview of this large-area imprint strategy. Therefore, only a brief summary will be given here. Two types of continuous imprinting exist, distinguished by the type of roller mold. Most often, the roller mold is patterned (Figure 2.15a). This can be done either directly.[157] or by patterning a flexible sheet mold[158-160] or shim and wrapping, or respectively mounting to a blank roller.[29, 161-163] Also, patterned molds spanning several rolls have been fabricated, so-called belt molds.[146] Alternatively, the roller mold can be used to apply pressure to a flat (Figure 2.15b) mold.[155] The latter suffers from similar scaling limitations as batch mode imprinting, in that the mold still has to be scaled to the full size of the substrate.[156] Furthermore, a classification in thermal[164] and UV-roller NIL (Figure 2.15c)[159, 160, 162] can be made like in batch patterning.

**Figure 2.15** Schematic illustrations of various types of roller NIL, with (a) a patterned roller mold and (b) a flat mold pressed by a non-patterned roller. Based on [155]. (c) Example of a typical UV roller NIL setup. Reprinted with permission from [156], Copyright © 2012, American Vacuum Society.

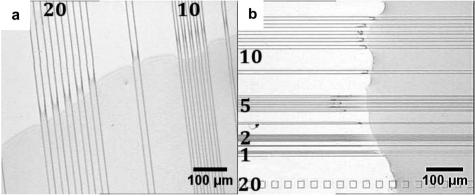

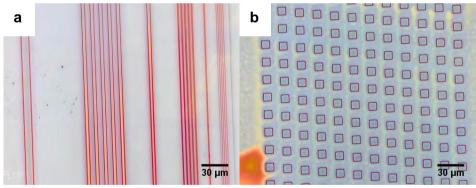

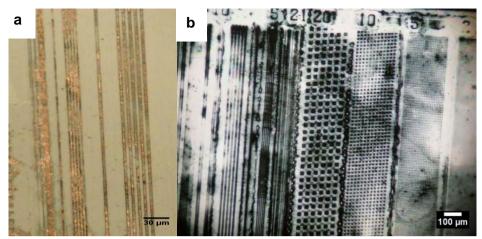

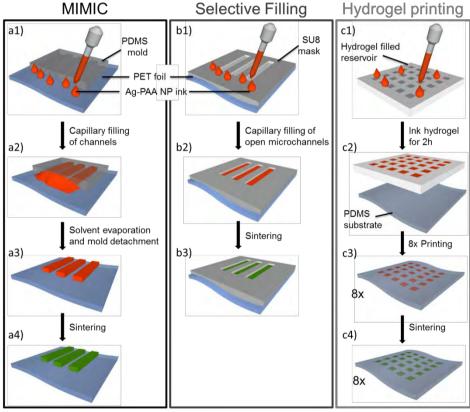

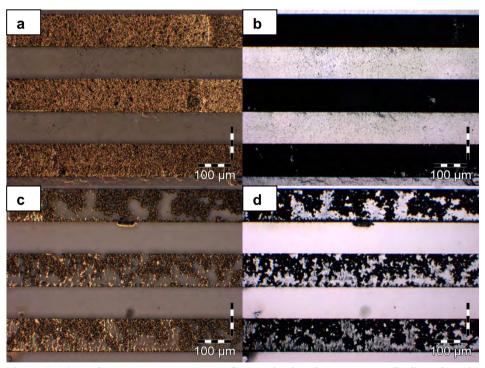

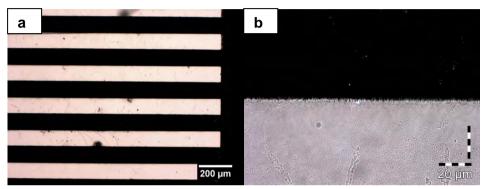

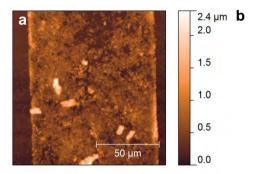

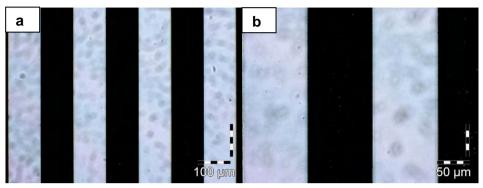

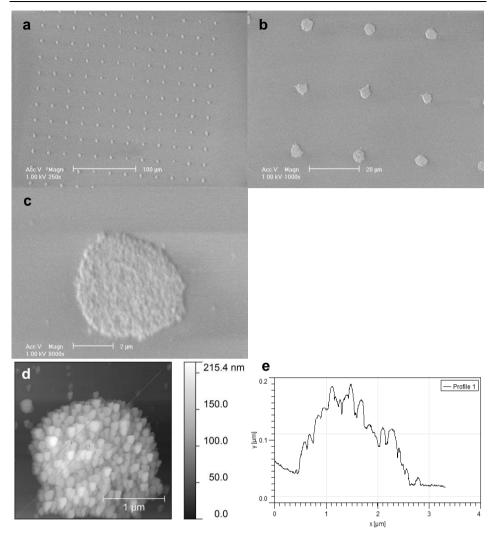

Since the first introduction of sub-micron and nanoscale thermal roller NIL in 1998<sup>[155]</sup> and UV roller NIL in 2006.<sup>[151, 165]</sup> the community improved the field immensely. Nowadays, seamless roller molds[157] can be fabricated and web tension control systems adjust the influences of temperature, vibration and thermal expansion. Furthermore, resist formulations (especially for UV roller NIL[146]), deposition systems and substrate coatings have been designed or optimized for uniform deposition and spreading, resulting in thin and reproducible layer thicknesses. With a cylindrical mold, pressure is only applied at the contact line between roller and substrate, allowing a considerable decrease of applied pressure and reduced gas entrapment. The distortion span in the resist layer, caused by local defects (e.g. dust) and surface contours or topography, is also reduced by the small contact line width between roller and substrate. Furthermore, the diameter of the cylinder with respect to the feature dimensions should be sufficiently large, in order to prevent damage by demolding to the just imprinted patterns.[166] A typical overlay resolution for a recently built R2R manufacturing line is around 5 µm.[167] With thermal roller NIL, mainly (nano-)gratings[29, 155, 164, 167] have been patterned. UV roller NIL has been applied in applications such as gratings, [146, 164] micro-lenses, [159, 160, 165] 3Dmicrostructures with undercuts,[166] anti-reflective coatings,[158] and flexible electronics.[150, 151]